LY68S3200 32M Bits Serial Pseudo-SRAM with SPI and QPI

## **REVISION HISTORY**

| <u>Revision</u> | Description                                                                                         | Issue Date   |

|-----------------|-----------------------------------------------------------------------------------------------------|--------------|

| Rev. 1.0        | Initial Issued                                                                                      | Sep.8. 2015  |

| Rev. 1.1        | Added <b>POWER UP INITIALIZATION</b> in page2                                                       | Dec.15. 2015 |

|                 | & COMMAND TERMINATION in page3                                                                      |              |

| Rev. 1.2        | Revised <b>QPI Mode : Write Operations(38h or 02h)</b> in page8                                     | Dec.25. 2015 |

|                 | Revised Operating Temperature to (-25 $^\circ \!\!\! \mathbb{C}$ to 85 $^\circ \!\!\! \mathbb{C}$ ) |              |

32M Bits Serial Pseudo-SRAM with SPI and QPI

## FEATURES

SPI compatible bus interface -Clock rate:

33MHz(max) for normal read 100MHz(max) for fast read

- -Mode: SPI/QPI Low power consumption:

- Operating current: 20mA(TYP.)

- Single 1.8V power supply

- Unlimited read/write cycle

- Fast write time as minimum cycle time

- 4M x 8-bit organization

- -1K byte per page

- High Reliability

- Green package available

- Package : 8-pin 150 mil SOP

### GENERAL DESCRIPTION

The LY68S3200 is a 32M-bit serial pseudo SRAM device organized as 4Mx8 bits. It is fabricated using very high performance, high reliability CMOS technology.

LY68S3200

The LY68S3200 is accessed via a simple Serial Peripheral Interface(SPI) compatible serial bus. Additionally, Quad Peripheral Interface(QPI) is supported if your application needs faster data rates. This device also supports unlimited reads and writes to the memory array.

The LY68S3200 operates from a single power supply of 1.8V and can offer high data bandwidth at 100MHz clock rate and Serial Quad interface.

The LY68S3200 offers 8-lead SOP package.

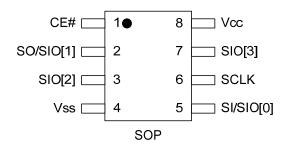

## PIN DESCRIPTION

| SYMBOL     | SPI MODE           | SQI MODE      |  |  |

|------------|--------------------|---------------|--|--|

| SI/SIOI[0] | Serial Input       | Serial I/O[0] |  |  |

| SO/SIO[1]  | Serial Output      | Serial I/O[1] |  |  |

| SIO[2]     | -                  | Serial I/O[2] |  |  |

| SIO[3]     | -                  | Serial I/O[3] |  |  |

| CE#        | Chip Select Input  |               |  |  |

| SCLK       | Clock Signal Input |               |  |  |

| Vcc        | Power Supply       |               |  |  |

| Vss        | Ground             |               |  |  |

# Pin Configuration

## ABSOLUTE MAXIMUN RATINGS\*

| PARAMETER                                              | SYMBOL          | RATING          | UNIT |

|--------------------------------------------------------|-----------------|-----------------|------|

| Voltage on V <sub>CC</sub> relative to V <sub>SS</sub> | V <sub>T1</sub> | -0.5 to 2.3     | V    |

| Voltage on any other pin relative to Vss               | V <sub>T2</sub> | -0.5 to Vcc+0.5 | V    |

| Operating Temperature                                  | TA              | -25 to 85       | °C   |

| Storage Temperature                                    | Tstg            | -65 to 150      | °C   |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to the absolute maximum rating conditions for extended period may affect device reliability.

32M Bits Serial Pseudo-SRAM with SPI and QPI

LY68S3200

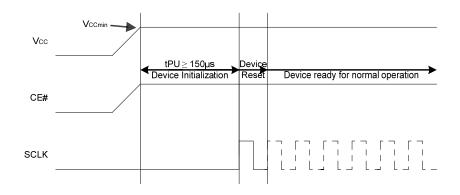

### **POWER-UP INITIALIZATION**

The LY68S3200 includes an on-chip voltage sensor used to start the self-initialization process. When V<sub>CC</sub> reaches a stable level at or above minimum V<sub>CC</sub>, the device will require 150µs to complete its self-initialization process. From the beginning of power ramp to the end of the 150µs period, SCLK should remain LOW, CE# should remain HIGH(track V<sub>CC</sub> within 200mV) and SI/SO/SIO[3:0] should remain LOW.

After the 150µs period, the device requires at least one clock during CE# high to properly reset the device, and then the device is ready for normal opearion.

## Command/Address Latching Truth Table

|                |      |     | 9    | SPI Mode      | e   |              |     | (    | QPI Mod       | e   |              |

|----------------|------|-----|------|---------------|-----|--------------|-----|------|---------------|-----|--------------|

| Command        | Code | Cmd | Addr | Wait<br>Cycle | DIO | Max<br>Freq. | Cmd | Addr | Wait<br>Cycle | DIO | Max<br>Freq. |

| Read           | 03h  | S   | S    | 0             | S   | 33           |     |      | N/A           |     |              |

| Fast Read      | 0Bh  | S   | S    | 8             | S   | 100          |     |      | N/A           |     |              |

| Quad Read      | EBh  | S   | Q    | 6             | Q   | 100          | Q   | Q    | 6             | Q   | 100          |

| Write          | 02h  | S   | S    | 0             | S   | 100          | Q   | Q    | 0             | Q   | 100          |

| Quad Write     | 38h  | S   | Q    | 0             | Q   | 100          | Q   | Q    | 0             | Q   | 100          |

| Enter QPI Mode | 35h  | S   | -    | -             | -   | 100          |     |      | N/A           |     |              |

| Exit QPI Mode  | F5h  |     |      | N/A           |     |              | Q   | -    | -             | -   | 100          |

Note: S = Serial IO, Q = Quad IO

LY68S3200

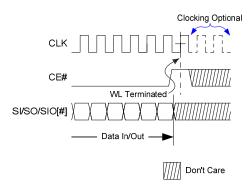

### **COMMAND TERMINATION**

All Reads & Writes must be completed by a clock pulse of CE# high immediately afterwards in order to terminate the active read/write wordline and set the device into standby. Not doing so will block internal refresh operations until the device sees the read/write wordline terminated.

| PARAMETER                           | SYMBOL           | TEST CON                                                               | DITION    | MIN.    | <b>TYP.</b> *1 | MAX.    | UNIT |

|-------------------------------------|------------------|------------------------------------------------------------------------|-----------|---------|----------------|---------|------|

| Supply Voltage                      | Vcc              |                                                                        |           | 1.65    | 1.8            | 1.95    | V    |

| Input High Voltage                  | VIH              |                                                                        |           | Vcc-0.4 | -              | Vcc+0.2 | V    |

| Input Low Voltage                   | VIL              |                                                                        |           | - 0.2   | -              | 0.4     | V    |

| Input Leakage Current               | lμ               | $V_{CC} \geqq V_{IN} \geqq V_{SS}$                                     |           | - 1     | -              | 1       | μA   |

| Output Leakage<br>Current           | Ilo              | $V_{CC} \ge V_{OUT} \ge V_{SS},$<br>Output Disabled                    |           | - 1     | -              | 1       | μA   |

| Output High Voltage                 | Vон              | I <sub>он</sub> = -0.2mA                                               |           | 0.8*Vcc | -              | -       | V    |

| Output Low Voltage                  | Vol              | I <sub>OL</sub> = +0.2mA                                               |           | -       | -              | 0.2*Vcc | V    |

| Average Operating                   | Icc1             | CE# $\leq 0.2$ ,<br>Others at 0.2V                                     | SPI@33MHz | -       | 6              | 15      | mA   |

| Power Supply Current I for Vcc_0 2V |                  | QPI@100MHz                                                             | -         | 20      | 30             | mA      |      |

| Standby Power<br>Supply Current     | I <sub>SB1</sub> | CE# $\geq$ V <sub>CC</sub> - 0.2V,<br>Others at 0.2V or V <sub>C</sub> | cc - 0.2V | -       | -              | 150     | μA   |

# DC ELECTRICAL CHARACTERISTICS

Notes:

1. Typical values are included for reference only and are not guaranteed or tested.

Typical valued are measured at V<sub>CC</sub> = V<sub>CC</sub>(TYP.) and T<sub>A</sub> =  $25^{\circ}$ C

### **CAPACITANCE** (T<sub>A</sub> = 25°C, f = 1.0MHz)

| PARAMETER                | SYMBOL | MIN. | MAX | UNIT |

|--------------------------|--------|------|-----|------|

| Input Capacitance        | CIN    | -    | 6   | pF   |

| Input/Output Capacitance | Cı/o   | -    | 8   | pF   |

Note : These parameters are guaranteed by device characterization, but not production tested.

## AC TEST CONDITIONS

| Input Pulse Levels                       | 0.2V to Vcc-0.2V                                                               |

|------------------------------------------|--------------------------------------------------------------------------------|

| Input Rise and Fall Times                | 1.5ns                                                                          |

| Input and Output Timing Reference Levels | Vcc/2                                                                          |

| Output Load                              | С <sub>L</sub> = 30pF + 1TTL, I <sub>OH</sub> /I <sub>OL</sub> = -0.2mA/+0.2mA |

# AC ELECTRICAL CHARACTERISTICS

| PARAMETER                         | SYM.             | LY68 | S3200 | UNIT             |

|-----------------------------------|------------------|------|-------|------------------|

| FARAIVIETER                       | 5 T IVI.         | MIN. | MAX.  | UNIT             |

| Clock Cycle Time                  | tclk@33MHz       | 30   | -     | ns               |

|                                   | tclk@100MHz      | 10   | -     | ns               |

| Clock low width                   | tc∟              | 0.45 | 0.55  | t <sub>CLK</sub> |

| Clock high width                  | tсн              | 0.45 | 0.55  | t <sub>CLK</sub> |

| Clock rise time                   | t <sub>R</sub>   | -    | 1.5   | ns               |

| Clock fall time                   | t⊧               | -    | 1.5   | ns               |

| CE# setup time to CLK rising edge | t <sub>CSP</sub> | 2.5  | -     | ns               |

| Setup time to active CLK edge     | ts               | 2.5  | -     | ns               |

| Hold time from active CLK edge    | tн               | 2    | -     | ns               |

| Chip disable to DQ output high-Z  | t <sub>HZ</sub>  | -    | 7     | ns               |

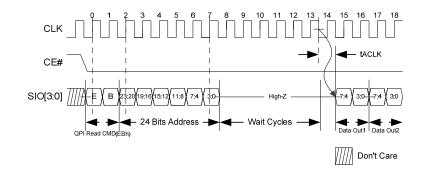

| CLK falling to output valid       | <b>t</b> ACLK    | -    | 7     | ns               |

| Output Hold from Clock falling    | toн              | 1.5  | -     | ns               |

| CE# low pulse width               | <b>t</b> CEM     | -    | 5     | us               |

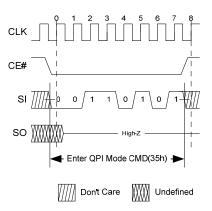

### **SPI MODE OPERATIONS**

The device powers up into SPI mode by default, but can also be switched into QPI mode.

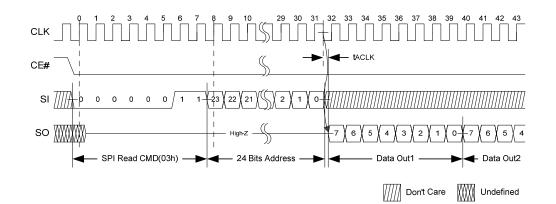

#### 1. SPI Mode : Read Operations

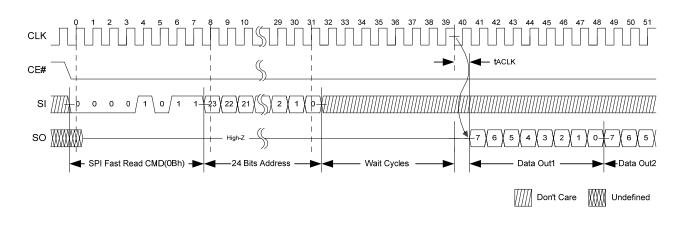

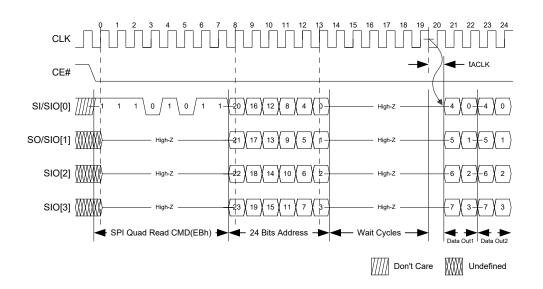

For all reads, data will be available t<sub>ACLK</sub> after the falling edge of CLK.

SPI Reads can be done in three ways:

- 1.1. 03h : Serial CMD, Serial IO, slow frequency

- 1.2. 0Bh : Serial CMD, Serial IO, fast frequency

- 1.3 EBh : Serial CMD, Quad IO, fast frequency

#### 1.1 SPI Read(03h)

### 1.2 SPI Fast Read(0Bh)

LY68S3200 32M Bits Serial Pseudo-SRAM with SPI and QPI

#### 1.3 SPI Quad Read(EBh)

Rev. 1.2

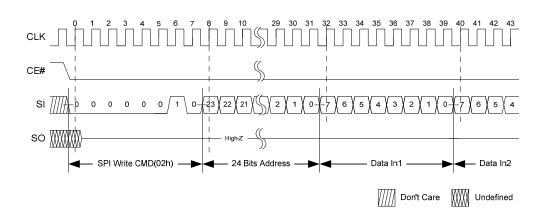

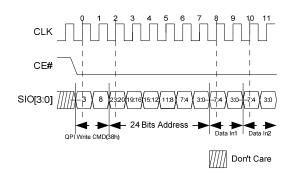

#### 2. SPI Mode : Write Operations

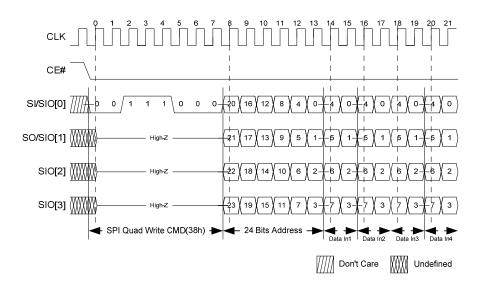

SPI Writes can be done in two ways:

- 2.1 02h : Serial CMD, Serial IO, slow frequency

- 2.1 38h : Serial CMD, Quad IO, fast frequency

#### 2.1 SPI Write(02h)

LY68S3200 32M Bits Serial Pseudo-SRAM with SPI and QPI

#### 2.2 SPI Quad Write(38h)

Rev. 1.2

### **QPI MODE OPERATIONS**

### 3. **<u>QPI Mode : Read Operations (EBh)</u>**

### 4. QPI Mode : Write Operations(38h or 02h)

*Lyontek Inc.* reserves the rights to change the specifications and products without notice. 2F, No. 17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan TEL: 886-3-6668838 FAX: 886-3-6668836

## 5. <u>QPI Mode : Enable Operation(35h)</u>

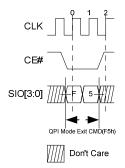

## 6. **QPI Mode : Quit Operation(F5h)**

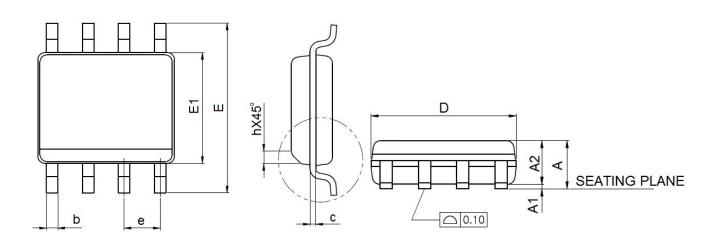

### PACKAGE OUTLINE DIMENSION

#### 8-pin 150mil SOP Package Outline Dimension

VARIATIONS (ALL DIMENSIONS SHOWN IN MM)

| SYMBOLS- | STANDARD |      |  |

|----------|----------|------|--|

| SIMBULS  | MIN.     | MAX. |  |

| А        |          | 1.75 |  |

| A1       | 0.10     | 0.25 |  |

| A2       | 1.25     |      |  |

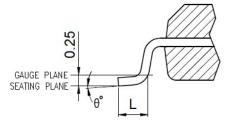

| b        | 0.31     | 0.51 |  |

| с        | 0.10     | 0.25 |  |

| D        | 4.90 BSC |      |  |

| E        | 6.00 BSC |      |  |

| E1       | 3.90     | BSC  |  |

| е        | 1.27 BSC |      |  |

| L        | 0.40     | 1.27 |  |

| h        | 0.25     | 0.50 |  |

| θ°       | 0        | 8    |  |

NOTES:

1.JEDEC OUTLINE : MS-012 AA REV.F (STANDARD) MS-012 BA REV.F (THERMAL)

2.DIMENSIONS "D" DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH, PROTRUSIONS AND GATE BURRS SHALL NOT EXCEED 0.15mm.

PER SIDE. 3.DIMENSIONS "E1" DOES NOT INCLUDE INTER-LEAD FLASH, OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25mm PER SIDE.

Lyontek Inc. reserves the rights to change the specifications and products without notice. 2F, No. 17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan TEL: 886-3-6668838 FAX: 886-3-6668836

## **ORDERING INFORMATION**

| Package Type | Maximum<br>Clock Rate(MHz) | Temperature<br>Range(℃) | Packing<br>Type | Lyontek Item No. |

|--------------|----------------------------|-------------------------|-----------------|------------------|

| 8-Pin        | 100                        |                         | Tube            | LY68S3200SL      |

| 150mil SOP   |                            | - <b>25℃~85℃</b>        | Tape Reel       | LY68S3200SLT     |

LY68S3200 32M Bits Serial Pseudo-SRAM with SPI and QPI

THIS PAGE IS LEFT BLANK INTENTIONALLY.